LS7366 카운터 데이터

엔코더 신호 A/ B 를 처리하는 방법으로 LSI/CSI 의 카운터 IC인 LS7366R을 사용하면 고속 카운트가 가능하며 하드웨어가 간단하여 시스템의 안정성이 향상된다.

LS7366R의 사양, SPI 인터페이스, 내부 레지스터 그리고 간단한 프로그램 방법에 관하여 알아 보기로 한다.

| 32-비트 시리얼 인터페이스(SPI) 쿼더래쳐 카운터 * 동작전압: 3V 에서 5.5V (VDD-VSS) * 5V 동작 시 최대 주파수 : 40MHz * 3V 동작 시 최대 주파수 : 20MHz * 32-비트 카운터(CNTR) * 32-비트 데이터 레지스터(DTR) 와 비교기 * 32-비트 출력 레지스터(OTR) * 2 개의 8 비트 모드 레지스터(MDR0, MDR1) 프로그램 가능한 기능모드 * 8 비트 명령 레지스터(IR) * 8 비트 상태표시 레지스터(STR) * 캐리, 보로우, 비교, 인덱스의 래치된 인터럽트 출력 * 비-쿼더래처 신호의 업/다운 카운트 * 카운트 영역지정(모듈로-N), 비-반복카운트(Non-recycle), 영역제한(Range-limit) 또는 프리-러닝 카운트 모드 * 8-비트, 16-비트, 24-비트, 32-비트 모드로 설정 가능한 동기(SPI)시리얼 인터페이스 * 3 가지의 패키지 타입: LS7366R (DIP), LS7366R-S (SOIC), LS7366R-TS (TSSOP) * 표준 SPI (Serial Peripheral Interface): MOSI, MISO, SS/ 그리고 SCK * 기타: 2, 3, 4 바이트 리드/라이트 시 최상위 바이트부터 바이트 내에서 최상위 비트(B7)부터 리드/라이트 한다. |

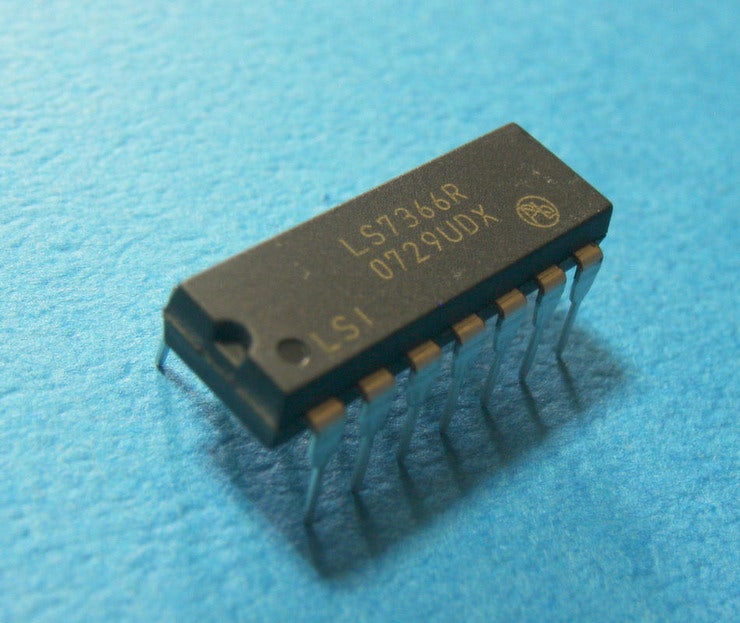

LS7366R

LS7366R 은 인크리멘털 인코더로부터 출력되는 쿼더래쳐 신호를 직접 수신하는 32-비트 CMOS 카운터 이다. A, B 상의 4 체배, 신호에 포함된 노이즈 필터링 그리고 엔코더나 외부 센서로부터 출력되는 인덱스 신호를 수신하여 카운터 프리 셋, 카운터 클리어 그리고 데이터 캡쳐등의 여러 가지 기능을 사용할 수 있다. Index 신호가 없는 로터리 엔코더에서 1 회전 펄스 수를 설정하여 자동적으로 회전 각도 값을 표시할 수 있는 N-modulo 카운트 기능을 가지고 있다. Index 신호의 인터럽트 출력이 가능하여 고 정밀도의 엔코더를 이용한 3 차원 측정기와 고속 서보 모션 제어기에 사용된다. 마이크로 프로세서와의 인터페이스는 MOTOROLA에서 제정한 시리얼 통신 방식의 SPI를 사용한다.

LS7366R은 마이크로 컨트롤러와의 통신을 위하여 4-선식 SPI(Serial Pheriperal Interface) 버스를 제공한다. LS7366R 은 SPI 규정에서 포지티브 클록(CPOL = 0), 데이터 선. 쉬프트 후 (CPHA = 0)에 맞추어져 있다. LS7366R에서 데이터 전송은 1 바이트부터 최대 5 바이트(설정에 따름)로 이루어진다.

데이터 전송 사이클은 SS/ 신호가 High 에서 Low로 변하면 시작한다. LS7366R 로 보내지는 첫번째 바이트는 언제나 IR 레지스터를 라이트하는 명령어이다. 그리고 2 번째 바이트부터 5 번째 바이트 까지는 데이터로 처리된다. 통신은 SS/ 입력이 Low 에서 High로 되면 종료된다.

SPI 통신

SPI 는 MOTOROLA (Freescale) 사에서 규정한 전이중 통신 방식의 시리얼 인터페이스이다.

4 개의 핀 SCK, MISO, MOSI, /SS 으로 구성되며 고속의 데이터 전송 시 사용된다. SPI는 쉬프트 레지스터를 이용한 통신 방법으로 대부분의 마이크로 프로세서에서 기본 기능으로 채택되어있으며 마이크로프로세서와 연결되는 많은 주변 기기 IC 에서 통신 방법으로 사용된다.

SPI 의 핀 구성

SCK : Serial Clock 데이터를 동기화 시키는 기준 클럭

MISO : Master Input Slave Output 마스터는 데이터 입력, 슬래이브는 데이터 출력

MOSI : Master Output Slave Input 마스터는 데이터 출력 슬래이브는 데이터 입력

/SS : Slave Select 슬레이브 셀렉트 (마스터가 슬래이브를 선택하기위한 신호)

SPI 는 프로그램시 3 가지를 고려하여야 한다.

클록 극성:

클록의 시작이 LOW -> HIGH 종료가 HIGH->LOW

클록의 시작이 HIGH->LOW 종료가 LOW->HIGH

클록위상:

CPHA = 0: 클록의 시작시 데이터를 샘플링하고 클록의 종료시 데이터 쉬프트된다.

CPHA = 1: 클록의 시작시 데이터를 쉬프트하고 클록의 종료시 데이터를 샘플링한다.

데이터 전송 순서:

바이트를 구성하는 8 개의 비트가 MSB가 선 송신/수신인지 LSB 가 선 송신/수신인지 결정한다.

MOTOROA 프로세서는 MSB 로 고정되어 있으나 LSB 선 송신/수신을 선택 가능한 마이크로 프로세서도 있으므로 확인하여야 한다.

카운터는 1,2,3 또는 4 바이트 카운터로 동작할 수 있다. N-바이트 카운터로 구성되면 CNTR, DTR, 그리고 OTR은 모두 N 바이트 레지스터로 설정된다. 여기서 N 은 1,2,3 또는 4 이다. 명령/데이터의 형식은 자동적으로 N-바이트 환경으로 일치된다. 예를 들어 카운터가 2 바이트로 구성되면 “DTR 쓰기” 는 명령어 바이트 다음에 2 바이트가 따라 오는 것으로 처리된다. 만약 카운터가 3 바이트 카운터로 구성되면 같은 명령에서 3 바이트의 데이터가 따르는 것으로 예상한다.

적당한 수의 바이트가 전송된 후 다른 데이터의 전송이 시작된다면 SS/ 입력이 High 에서 Low 로 전환되어 새로운 명령 사이클이 개시되기 전까지 무시된다.

카운터는 두개의 모드 레지스터 MDR0 와 MDR1 레지스터를 라이팅하여 여러 개의 다른 동작 모드로 동작하도록 프로그램 가능하다.

LS7366R의 핀사양

LS7366R은 14Pin 으로 구성되어있다, 3 개의 패키지 버전(DIP, SOP, TSSOP)이 있으나 핀수와 핀번호에 정해진 기능은 모두 동일하다.

A(Pin 12)-입력, B(Pin 11)-입력

인크리멘탈 엔코더로부터 출력되는 A, B 쿼더래쳐 신호 입력이며 LS7366R의 입력으로 직접 연결한다. 이 입력은 90° 위상 차이가 있다. A상 신호와 B상 신호는 서로 상대적이다. A 신호의 변화가 B 신호의 변화보다 시간적으로 앞서면 카운터 값은 증가하며 반대로 늦으면 카운터 값은 감소한다. A와 B 신호는 내장된 디지털 필터를 거치게 되며 업/다운 방향과 카운트 클록 신호로 분해된다. 비-쿼더래쳐 모드에서 A 는 카운트 펄스 입력으로 B 는 방향 입력으로 동작한다. (B = High: 업 카운트 B=Low: 다운 카운트) 비-쿼더래쳐 모는 입력이 필터 처리되지 않는다.

INDEX/ (Pin 10)-입력

INDEX/ 는 인크리멘털 엔코더로 부터 출력된 인덱스 신호에 의하여 직접 구동 되도록 프로그램 가능하다. MDR0를 프로그램하여 터치 프리셋 (DTR로부터 CNTR에 로드), 터치 리셋 (CNTR을 0으로), 캡쳐(CNTR로부터 OTR 에 로드) 그리고 Index을 사용하지 않도록 할 수 있다.

쿼더래쳐 모드에서 INDEX/ 입력은 동기 또는 비동기 모드로 동작하도록 프로그램할 수 있다. 비동기 모드에선 A, B 의 상태에 관계없이 Index 가 Low 레벨이 되면 즉시 Index 동작(프리셋, 리셋 또는 캡쳐)이 실행된다. 동기모드 일 때 INDEX/ 입력은 입력 A 와 B 를 샘플링 하기 위한 클록에서 샘플링 된다. A 와 B 입력은 위상관계를 만족하여야 한다. A 와 B 가 동시에 High 이거나 동시에 Low 인 동안에 Index 는 Low 를 유지하고 있어야 한다. 비-쿼더래쳐 모드에서 INDEX/ 입력은 샘플링하지 않으며 어느 위상이든 직접 적용된다.

fCKi(Pin 2)-입력, fCKo(Pin 1)-출력

이 두 핀에 A, B 그리고 INDEX/ 입력을 필터링 하기위한 기본 클럭을 발생하기 위하여 크리스털을 연결한다. 크리스털 대신에 fCKi 에 외부 클록을 연결할 수 있다.

fCKi 에 입력되는 주파수는 2 분주(MDR0<B7> = 1) 또는 1 분주(MDR0<B7> = 0)하여 필터 주파수 ff가 되며 A, B 와 INDEX/ 입력의 정확한 필터링이 되기 위하여 A, B 상 주파수보다 4배 이상 커야 한다.

SS/ (Pin4)-입력

SS/ 가 High에서 Low로 변할 때 LS7366이 양방향 시리얼 통신이 되도록 한다. Low 에서 High 로 되면 시리얼 통신은 금지되며 MISO 핀은 하이-임피던스 상태가 된다. 이것은 여러 개의 슬래이브 유닛이 가능하게 한다.

CNT_EN (Pin13)-입력

CNT_EN 이 High 이면 카운트 가능 상태로 된다. 이 핀이 Low 이면 카운트 정지이다. 이 입력은 내부적으로 Pull-Up 저항이 부착되어 있어 이 핀을 사용하지 않을 때 개방 상태로 두어도 된다.

LFLAG/ (Pin8)-출력, DFLAG/ (Pin 9)-출력

LFLAG/ 와 DFLAG/ 는 Carry( 카운터 오버 플로우)가 발생, Borrow(카운터 언더 플로우) 비교 (CNTR = DTR) 그리고 INDEX 가 발생할 때 플래그가 출력되도록 설정이 가능한 출력 이다.

LFALG/는 오픈 드레인이며 래치 출력이다. 반면에 DFLAG/는 푸쉬-풀 출력 이다. LFLAG/는 여러 개의 슬래이브 구성에서 묶여질 수 있다(Wired-OR). 그러므로 하나의 프로세서가 여러 개의 LS7366R에서 발생한 인터럽트 처리 가능하다. 활성화된 LFLAG/스위치가 0 으로 되면 스태터스 레지스터 STR를 클리어 하여 하이 임피던스 상태로 복귀된다. 마이크로 프로세서에서 이 핀을 인터럽트 처리하려면 LOW 레벨 모드로 설정한다.

DFLAG/ 는 Carry, Borrow, Compare 그리고 INDEX 상태에 즉시 low 상태로 된다.( Carry, Borrow, Compare 그리고 INDEX 상태에서 벋어나면 즉시 High 상태로 복귀된다. 마이크로 프로세서에서 이 핀을 인터럽트 입력 처리 하려면 에지 트리거 모드로 설정한다.

LFALG/와 DFLAG/는 MDR1에서 설정 한다.

MOSI (Pin 7)-입력

마스터가 출력한 데이터를 수신한다. SS/ 가 Low 상태에서만 입력한 데이터가 유효하다.

MISO (Pin 6)-출력

LS7366R로부터 데이터가 출력되는 핀이다. MISO는 SS/ 가 High 가 되면 하이-임피던스 상태가 되어 여러 개의 슬래이브 유닛이 Wired-OR 출력이 가능하도록 한다.

SCK (Pin 5)-입력

SCK 입력은 MOSI, MISO의 데이터 전송 시 LOW->HIGH 이며 쉬프트는 HIGH->LOW 일때 실행하는 MOTOROLA SPI 사양의 Mode 0 조건으로 동작한다. LS7366R은 항상 슬래이브 모드로 동작하므로 SCK 신호는 호스트 마이크로 프로세서에서 공급하여야 한다.

LS7366R의 레지스터:

다음 열거되는 것이 LS7366R의 내부 레지스터 이다.

파워-온 리셋되면 레지스터 DTR, CNTR, STR, MDR0, MDR1 은 0 으로 리셋된다.

DTR. 소프트웨어 설정 가능한 DTR 은 8, 16, 24 또는 32 비트 입력 데이터 레지스터이며 MOSI 로부터 직접 라이트 될 수 있다. DTR 데이터는 32-비트 카운터(CNTR)로 부터 프로그램 제어 또는 Index 신호에 의한 하드웨어 적으로 CNTR로 전달될 수 있다. DTR 은 클리어 명령에의 하여 클리어 될 수 있다. DTR의 주 용도는 CNTR 레지스터를 프리셋 하는 것이다. (CNTR로 직접 라이트 할 수 없다.) 그리고 모듈로-N 모드 동작 시 DTR 은 모듈로 N 값, 영역-제한 모드 동작 시 제한 데이터를 저장하고 있다. 비교 동작에서 비교 플래그가 세트되면 DTR 은 CNTR 과 비교 된다. 4 바이트 모드로 설정된 경우 B31-B24, B23-B16, B15-B8 그리고 B7-B0 의 순서로 라이트 한다.

CNTR. 소프트웨어 설정 가능한 CNTR 은 8, 16, 24 또는 32-비트 업/다운 카운터이며 A 와 B 입력에 가해진 쿼더래쳐 신호를 1 체배, 2 체배 또는 4 체배(MDR0 B1, B1에서 선택)하여 얻어진 Up/Down 펄스를 카운트 한다. CNTR 은 클리어 하거나 DTR로부터 데이터를 가져올 수 있다(Pre-Set). CNTR은 마이크로 프로세서에서 데이터를 읽기(MISO 핀으로 출력)만 가능하며 쓰기는 할 수 없다. 4 바이트 모드로 설정된 경우 데이터를 읽을 때 B31-B24, B23-B16, B15-B8 그리고 B7-B0 의 순서로 출력된다.

OTR. 소프트웨어 설정 가능한 OTR은 8, 16, 24 또는 32-비트 레지스터 이며 MISO 를 통하여 출력된다. 주로 Index 펄스에 의하여 CNTR 값을 래치한 후 읽어내는 용도로 사용한다.

STR. 8-비트의 상태 레지스터이며 카운트와 관련된 정보를 저장하고 있다.

STR. 8-비트의 상태 레지스터이며 카운트와 관련된 정보를 저장하고 있다.

CY: 캐리(CNTR 오버플로우) 래치 (CNTR 이 0xFFFFFFFE에서 0xFFFFFFFF 로 되면 발생) BW: 보로우(CNTR 언더플로우) 래치 (CNTR 0x00000001 에서 0x00000000 로 되면 발생) CMP: 비교 (CNTR = DTR) 래치 IDX: 인덱스 래치(Index 핀이 High -> Low) CEN: 카운트 인에이블 상태: 0: 카운트 정지, 1: 카운트 가능 PLS: 파워 손실 표시 래치: 파워 업시 세트 U/D: 카운트 방향 표시: 0: 카운트 다운, 1: 카운트 업 S: 부호비트 1: 음수 0: 양수 |

IR. 8-비트 레지스터인 IR은 MOSI 핀으로 입력되는 데이터열로 부터 명령어를 페치하여 선택한 레지스터를 조작한다. 명령은 CLR(Cear), RD(Read), WR(Write) 그리고 LOAD의 4 명령 이며 레지스터는 MDR0, MDR1, DTR, CNTR, OTR 그리고 STR의 6 개 레지스터이다.

B2 B1 B0 = XXX (사용하지 않음) B5 B4 B3 = 000 : 선택 하지 않음 = 001 : MDR0 선택 = 010 : MDR1 선택 = 011 : DTR 선택 = 100 : CNTR 선택 = 101 : OTR 선택 = 110 : STR 선택 = 111 : 선택하지 않음 B7 B6 = 00 : 레지스터 CLR = 01 : 레지스터 RD = 10 : 레지스터 WR = 11 : 레지스터 LOAD |

CLR, RD, WR 그리고 LOAD 와 레지스터를 조합한 명령어 | |||||

바이트 수 | 명령 코드 | 레지스터 | IR(Binary) | IR(Hex) | 동작 |

1 | CLR | MDR0 MDR1 DTR CNTR OTR STR | 00001000 00010000 00100000 00110000 | 0x08 0x10 0x20 0x30 | MDR0 를 0 으로 클리어 MDR1 를 0 으로 클리어 CNTR 을 0 으로 클리어 STR 을 0 으로 클리어 |

2 에서 5 | RD | MDR0 MDR1 DTR CNTR OTR STR | 01001000 01010000 01100000 01101000 01110000 | 0x48 0x50 0x60 0x68 0x70 | MDR0 을 TXD(MISO)에 의하여 시리얼 출력 MDR1 을 TXD(MISO)에 의하여 시리얼 출력 CNTR을 OTR 로 전달하고 MISO에 출력 OTR 을 TXD(MISO)로 시리얼 출력 STR 을 TXD(MISO)로 시리얼 출력 |

2 에서 5 | WR | MDR0 MDR1 DTR CNTR OTR | 10001000 10010000 10011000 10101000 | 0x88 0x90 0x98 0xA8 | MOSI를 통하여 MDR0에 시리얼 데이터 라이트 RXD(MOSI를 통하여 MDR1에 시리얼 데이터 라이트 RXD(MOSI를 통하여 DTR에 시리얼 데이터 라이트 |

1 | LOAD | STR MDR0 MDR1 DTR CNTR OTR | 11100000 11101000 | 0xE0 0xE8 | DTR 을 CNTR 로 파라렐 전송 CNTR 을 OTR 로 파라렐 전송 |

MDR0. 모드 레지스터 MDR0 는 8 비트 리드/라이트 레지스터 이며 LS7366R 의 동작모드를 설정한다. MDR0에서 Index 신호가 없는 로터리 엔코더에서 1 회전 펄스 수를 입력하여 자동적으로 기준 각도(0 도)를 표시할 수 있는 N-modulo 카운트 기능이 설정 가능하다. MDR0는 파워-업 시 0으로 클리어 된다.

B1 B0 = 00: 비-쿼더래쳐 카운트 모드. (A = 클록, B = 방향). = 01: x1 쿼더래쳐 카운트 모드( 쿼더래쳐 사이클당 1 카운트) = 10: x2 쿼더래쳐 카운트 모드( 쿼더래쳐 사이클당 2 카운트) = 11: x4 쿼더래쳐 카운트 모드( 쿼더래쳐 사이클당 4 카운트) B3 B2 = 00: Free-running 카운트 모드 = 01: Single-Cycle 카운트 모드(카운터는 캐리나 보로우가 발생하면 동작을 멈춘다. 리셋이나 프리셋에 의하여 재 카운트 가능 = 10: Range-Limit 카운트 모드( 0 과 DTR 설정 값 내에서만 카운트 가능하다) = 11: Modulo-n 카운트 모드이며 CNTR 은 DTR 값이되면 0 이된다. B5 B4 = 00: 인덱스 기능 사용하지 않음 = 01: 인덱스 펄스가 입력되면 DTR 값을 CNTR 로 로드한다. 원점 신호에 의한 프리셋으로 사용한다. = 10: 인덱스 펄스가 입력되면 CNTR 을 0 으로 초기화 한다. 원점 신호에 의한 절대 위치 설정 = 11: 인덱스 펄스가 입력되면 CNTR 값을 OTR 로 로드한다. 3 차원 측정기에서 프르부 터치에 의한 좌표 측정 시 사용한다. |

MDR1: Mode Register 는 8-비트의 읽기/쓰기 가능 레지스터이다. 추가적인 모드 설정을 위하여 MDR0 에 부가된다. MDR1 레지스터는 전원 투입시 0 으로 클리어된다.

B1 B0 = 00: 4-바이트 카운트 모드 = 01: 3-바이트 카운트 모드 = 10: 2-바이트 카운터 모드 = 11: 1-바이트 카운트 모드 B2 = 0: Enable counting = 1: Disabling counting B3 = : 사용하지 않음 B4 = 0: NOP (아무 동작하지 않음) = 1: IDX 입력시 FLAG 세트(STR 레지스터의 B4) B5 = 0: NOP = 1: DTR 과 CNTR 이 일치할 때 FLAG 세트(STR 레지스터의 B4) B6 = 0: NOP = 1: 보로우(BW) 발생시 FLAG 세트(STR 레지스터의 B4) B7 = 0: NOP = 1: 캐리(CY) 발생시 FLAG 세트(STR 레지스터의 B4) |

LS7366R의 간단한 테스트 회로구성

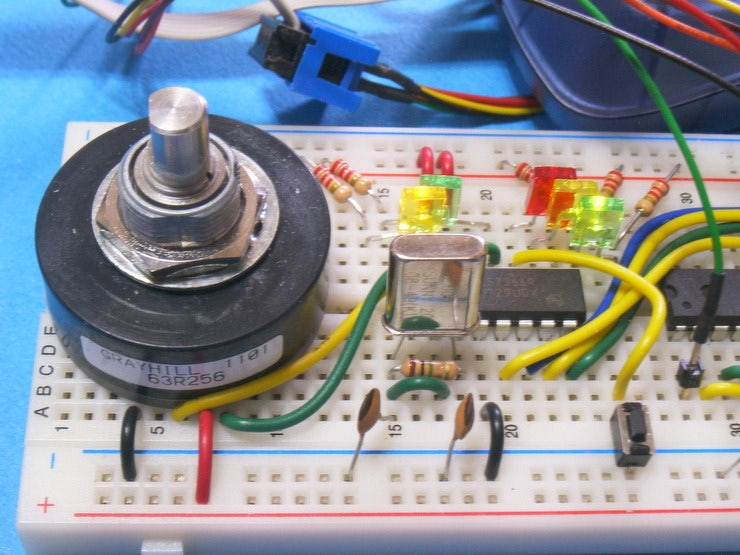

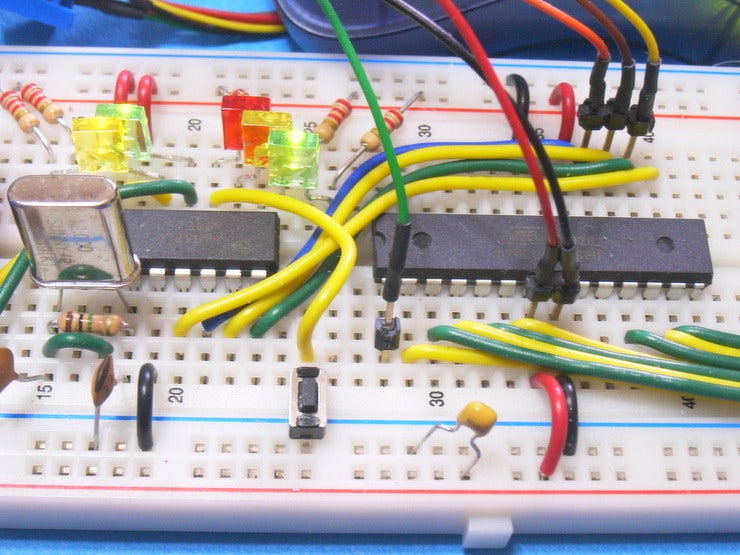

브레드 보드에 로터리 엔코더, LS7366R, ATMEL 사의 8ㅂ트 프로세서 ATMega8 을 실장하여 테스트 보드를 만든 것이다. LED 8 개를 사용하여 카운트 값의 변화를 볼 수 있다. Index 신호는 택트 스위치를 사용하여 입력한다. 프로세서의 클럭은 내장 RC 오실레이터 8MHz 로 퓨즈비트에서 설정한다.

프로그램 다운로드는 ATMEL 의 AVRISP-MK2 를 이용하였다.

LS7366R 프로그래밍 예

1 회전에 256 펄스를 출력하는 엔코더의 A, B상 신호를 LS7366R에서 카운트하고 ATMEL 사의 ATMega8 프로세서에서 8 개의 LED에 1 바이트 카운트 값을 표시한다. 그림-5는 테스트용 회로도이며 그림-6 은 브레드 보드에 LS7366R 테스트 회로를 구성한 것이다. 소프트웨어 개발환경은 미국 ImageCraft 사의 ICC-AVR C 데모 버전 컴파일러를 사용하였다.

그림-7은 C로 작성한 LS7366R 테스트용 프로그램이다.

마이크로 프로세서가 전원 ON 되면 프로세서의 내부 그리고 PORT 입/출력 등의 초기화를 실행한다. 다음으로 LS7366R을 초기화 한다. 그리고 LS7366R의 카운터(CNTR)값을 읽어 PORTD 에 출력을 반복한다.

Line19 init_devices() 에서 PORT의 방향(입력/출력) 및 초기 값(High/Low)설정은 SPI에 맞도록 한다. /SS 핀은 출력/HIGH, CLK 핀은 출력/LOW, MOSI 핀은 출력, MISO 핀은 입력으로 되도록 설정한다. SPI 의 모드는 SPI Mode = 0인 CPOL = 0, CPHA = 0으로 설정한다. 데이터는 MSB(최상위 비트) 가 먼저 전송되도록 설정한다.

Line13 의 unsigned char shift_data_io(unsigned char c)는 1 개의 바이트를 SPI 를 통하여 내보내고 1 개의 바이트를 수신하여 반환하는 함수이다. ATMega8 의 데이터 시트의 예제 코드를 인용한 것이다.

Line19 void init_LS7366R(void)는 LS7366R을 초기화 시킨다. MDR0 를 4체배 모드로 MDR1에서 1 바이트 카운트 모드로 설정한다. 그리고 CNTR, STR 레지스터를 클리어한다.

Line64 의 while 무한 루프문에서 CNTR 을 읽어 ATMega8 의 PORTD 에 라이트한다.

Line66 은 CNTR 값을 읽기 위한 명령어를 0x60을 IR 로 보낸 것이다.

Line67 은 LS7366R의 MISO 핀에서 출력되는 데이터를 PORTD 에 라이트한다. 0x00 는 SPI 통신 특성상 어떠한 데이터라도 출력되어야 하므로 0x00 을 보낸 것 이므로 LS7366R에서 무시되므로 다른 어떤 값이라도 관계없다

PORTD 핀(7~0)이 0 상태에서 LED 가 ON 된다. 엔코더를 회전시키면 8 개의 LED 에 CNTR 카운터의 변화를 확인할 수 있다.

http://www.fajournal.com/

[출처]

댓글 없음:

댓글 쓰기